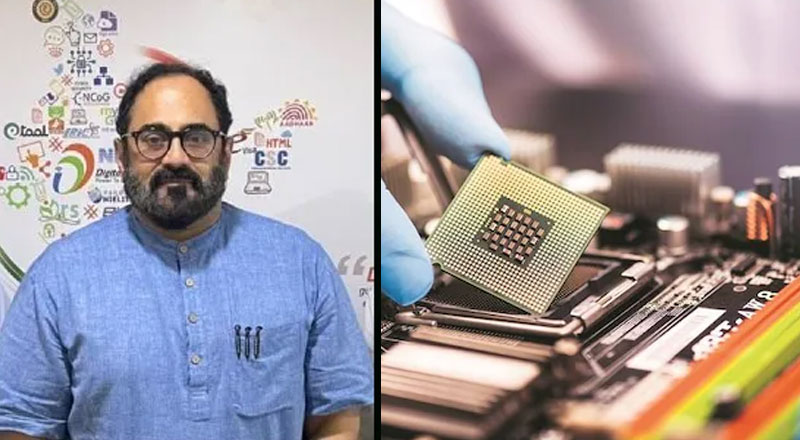

Addressing the media at the Semicon India 2022 conference, Minister of State for Electronics and IT Rajeev Chandrasekhar said that the government will review norms of the design linked incentive (DLI) program which is expected to support 100 companies involved in product design in the semiconductor space as part of a Rs 76,000 crore scheme for developing the electronic chip ecosystem in the country.

Chandrasekhar said, “Whether the DLI norms need to be modified… We have got some feedback from this conference that maybe the DLI has been designed to be very narrow. Maybe there is a cap on funding that is too restrictive. We will examine all that.” He also said the scheme will continue to be in place to support all product design projects and startups, among others.

The scheme provides for reimbursement of up to Rs 30 lakh per application for MPW (multi-project wafer) fabrication of design and post-silicon validation activities; reimbursement of up to 50 percent of the eligible expenditure subject to a ceiling of Rs 15 crore per application for designing semiconductor goods; and reimbursement of 6 to 4 percent of net sales of designed semiconductor goods over 5 years subject to a ceiling of Rs 30 crore.

“I want to say this very clearly that the USD 10 million package of the Rs 76,000 crore package is for the ecosystem and design and innovation is a very important part of the ecosystem. Talent is a very important part of the ecosystem. There is a need to sort of redesign some of those pieces, we will do it,” Chandrasekhar added.

At the Semicon India 2022 conference, seven memorandums of understanding (MoUs) were signed between government organisations and technology companies. MoUs were signed between Cyient, WiSig Networks and IIT Hyderabad to enable mass production of “5G Narrowband-IoT- the Koala Chip, Architected and Designed in India”.

Signalchip Innovations, Ministry of Electronics and IT (MeitY) and the Centre for Development of Advanced Computing (C-DAC) signed an agreement for not only design and manufacture but also deployment and maintenance of 10 lakh Integrated NavIC (Navigation with Indian Constellation) and GPS Receivers. CDAC announced partnership with Synopsys, Cadence Design Systems, Siemens EDA and Silvaco for making available their Electronic Design Automation (EDA) tools and design solutions for Chips to Startup (C2S) Programme being implemented by CDAC.